# Selected docket entries for case 18–1768

Generated: 04/10/2019 20:33:34

| Filed      | <b>Document Description</b> | Page | Docket Text                                                                                                                                                                                                                                                               |

|------------|-----------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07/10/2018 | 22 ApInt/Pet Opening Brief  |      | BRIEF FILED for Appellant Polaris Innovations Limited [21]. Number of Pages: 60. Service: 07/10/2018 by email. The paper copies of the brief should be received by the court on or before 07/18/2018. Appellee Kingston Technology Company, Inc. brief is due 08/20/2018. |

|            |                             |      | [535025] [CFT]                                                                                                                                                                                                                                                            |

Case: 18-1768 Document: 22 Page: 1 Filed: 07/10/2018 (2 of 158)

#### 2018-1768

# IN THE UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

#### POLARIS INNOVATIONS LIMITED.

Appellant

v.

#### KINGSTON TECHNOLOGY COMPANY, INC.

Appellee

APPEAL FROM THE UNITED STATES PATENT AND TRADEMARK OFFICE, PATENT TRIAL AND APPEAL BOARD NO. IPR2016-01621

# PRINCIPAL BRIEF OF APPELLANT POLARIS INNOVATIONS LIMITED

Matthew D. Powers

Azra Hadzimehmedovic

Alex Chan

Yi Chen

TENSEGRITY LAW GROUP, LLP

555 Twin Dolphin Drive, Suite 650

Redwood Shores, CA 94065

Telephone: (650) 802-6000

Facsimile: (650) 802-6001

Kenneth Weatherwax Nathan Lowenstein LOWENSTEIN & WEATHERWAX LLP 1880 Century Park East, Suite 815 Los Angeles, California 90067 Telephone: (310) 307-4500 Facsimile: (310) 307-4509

Counsel for Appellant Polaris July 10, 2018

Innovations Limited

Case: 18-1768 Document: 22 Page: 2 Filed: 07/10/2018

(3 of 158)

#### **CERTIFICATE OF INTEREST**

Counsel for Appellant Polaris Innovations Limited ("Polaris") in Appeal No. 2018-1768 certifies the following:

1. The full name of every party or amicus represented by me is:

Polaris Innovations Limited.

2. The name of the real party in interest (if the party named in the caption is not the real party in interest) represented by me is:

Quarterhill Inc.

3. All parent corporations and any publicly held companies that own 10 percent or more of the stock of the party or amicus curiae represented by me are:

Wi-LAN, Inc.

4. The names of all law firms and the partners or associates that appeared for the party or amicus now represented by me in the trial court or agency or are expected to appear in this court are:

Parham Hendifar, Lowenstein & Weatherwax LLP

- 5. The title and number of any case known to counsel to be pending in this or any other court or agency that will directly affect or be directly affected by this court's decision in the pending appeal are:

- Polaris Innovations Limited v. Kingston Technology Company, Inc., 8:16-cv-00300 (C.D. Cal).

Dated: July 10, 2018 /s/ Matthew D. Powers

Matthew D. Powers

# TABLE OF CONTENTS

| TAB  | LE | OF CONTENTS                                                                                                                                                                             | ii |

|------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| TABl | LE | OF AUTHORITIESi                                                                                                                                                                         | V  |

| I.   | S  | TATEMENT OF JURISDICTION                                                                                                                                                                | 1  |

| II.  | S  | ΓATEMENT OF THE ISSUES                                                                                                                                                                  | 1  |

| III. | S  | ΓATEMENT OF THE CASE AND FACTS                                                                                                                                                          | 2  |

| A.   |    | Introduction                                                                                                                                                                            | 2  |

| В.   |    | The 057 Patent                                                                                                                                                                          | 2  |

| C.   |    | The Inter Partes Review                                                                                                                                                                 | 9  |

| IV.  | SI | UMMARY OF ARGUMENT1                                                                                                                                                                     | 8  |

| V.   | A  | RGUMENT2                                                                                                                                                                                | 0  |

| A.   |    | Legal Standards                                                                                                                                                                         | .0 |

| B.   |    | The Board Applied An Overbroad Interpretation Of "Signal Indicative Of The Temperature Of The DRAM Array" To Include Signals Not Outputtable To External Circuitry Via A Connection Pin |    |

| C.   |    | The Board's Decision To Institute And Cancel Claims On A Ground Not Identified In The Petition Requires Reversal                                                                        |    |

|      | 1. | The Board Cannot Institute An IPR Or Cancel Claims On An Unpetitioned Ground                                                                                                            | 28 |

| ,    | 2. | The Board Impermissibly Instituted IPR And Cancelled The Diode Claims On An Unpetitioned Ground                                                                                         | 2  |

| •    | 3. | The Sua Sponte Ground Lacks Substantial Supporting Evidence3                                                                                                                            | 8  |

(5 of 158)

|   | D.   | The Board Improperly Found The Non-Diode Claims Obvious Over Atkinson And Broadwater                                                                                            | 42 |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.   | No Substantial Evidence Supports The Board's Determination That Atkinson Teaches Overheating Prevention                                                                         | 42 |

|   | 2.   | No Substantial Evidence Supports The Determination That Atkinson Would Have Added Broadwater's Pin To Maximize Power Saving                                                     | 47 |

|   | E.   | The Board Improperly Ignored The Objective Indicia Of Nonobviousnes Relevant to All Cancelled Claims                                                                            |    |

|   | F.   | The Board Members Could Not Constitutionally Issue A Final Agency Decision Eliminating Patent Rights Without Having Been Appointed By The President And Confirmed By The Senate |    |

|   | 1.   | PTAB Judges Who Decide IPRs Are Incontestably "Officers" Of The United States Under The Constitution's Appointments Clause                                                      | 53 |

|   | 2.   | Because PTAB Judges Issue Final IPR Decisions Eliminating Patent Rights, They Must Be "Principal Officers"                                                                      | 56 |

|   | 3.   | The Final Written Decision Must Be Set Aside On The Basis Of The Board Members' Improper Appointment                                                                            | 59 |

| V | I. C | CONCLUSION AND STATEMENT OF RELIEF SOUGHT                                                                                                                                       | 50 |

## TABLE OF AUTHORITIES

| Page                                                                                      | e(s) |

|-------------------------------------------------------------------------------------------|------|

| Cases                                                                                     |      |

| Arendi S.A.R.L. v. Apple Inc.,<br>832 F.3d 1355 (Fed. Cir. 2016)                          | .39  |

| Ariosa Diagnostics v. Verinata Health, Inc., 805 F.3d 1359 (Fed. Cir. 2015)               | .21  |

| Ass'n of Am. R.R. v. United States DOT,<br>821 F.3d 19 (D.C. Cir. 2016)                   | .57  |

| Buckley v. Valeo,<br>424 U.S. 1 (1976)52,                                                 | , 54 |

| Collins v. United States,<br>14 Ct. Cl. 568 (1878)                                        | .57  |

| Cuozzo Speed Techs., LLC v. Lee,<br>136 S. Ct. 2131 (2016)                                | .55  |

| D'Agostino v. MasterCard Int'l, Inc.,<br>844 F.3d 945 (Fed. Cir. 2016)                    | .27  |

| DePuy Spine, Inc. v. Medtronic Sofamor Danek, Inc., 567 F.3d 1314 (Fed. Cir. 2009)        | .49  |

| Dickinson v. Zurko,<br>527 U.S. 150 (1999)                                                | .21  |

| Elbit Systems of America, LLC v. Thales Visionix, Inc.,<br>881 F.3d 1354 (Fed. Cir. 2018) | .47  |

| Free Enter. Fund v. PCAOB,<br>561 U.S. 477 (2010)                                         | .56  |

| Freytag v. Commissioner,<br>501 U.S. 868 (1991)53,                                        | , 54 |

(7 of 158)

| Honeywell Int'l Inc. v. Mexichem Amanco Holding S.A. de C.V., 865 F.3d 1348 (Fed. Cir. 2017)                  |

|---------------------------------------------------------------------------------------------------------------|

| HTC Corp. v. Cellular Comm'ns Equipment, LLC,<br>877 F.3d 1361 (Fed. Cir. 2017)22                             |

| CON Health & Fitness, Inc. v. Strava, Inc.,<br>849 F.3d 1034 (Fed. Cir. 2017)                                 |

| In re Cyclobenzaprine Hydrochloride Extended–Release Capsule Patent Litig., 676 F.3d 1063 (Fed. Cir. 2012))52 |

| In re Hodges,<br>882 F.3d 1107 (Fed. Cir. 2018)25, 26                                                         |

| In re Leithem, 661 F.3d 1316 (Fed. Cir. 2011)35                                                               |

| In re Magnum Oil Tools Int'l, Ltd.,<br>829 F.3d 1364 (Fed. Cir. 2016)                                         |

| In re NuVasive, Inc.,<br>841 F.3d 966 (Fed. Cir. 2016)                                                        |

| <i>In re Sullivan</i> , 498 F.3d 1345 (Fed. Cir. 2007)51                                                      |

| In re Wright, 848 F.2d 1216 (Fed. Cir. 1988)50                                                                |

| Intelligent Bio-Sys., Inc. v. Illumina Cambridge, Ltd., 821 F.3d 1359 (Fed. Cir. 2016)                        |

| Intercollegiate Broad. Sys., Inc. v. Copyright Royalty Board, 684 F.3d 1332 (D.C. Cir. 2012)                  |

| Lighting Ballast Control LLC v. Philips Elecs. N. Am. Corp., 744 F. 3d 1272 (Fed. Cir. 2014)21                |

(8 of 158)

| Lucia v. SEC,<br>No. 17-130, 2018 U.S. LEXIS 3836, 585 U.S (June 21, 2018).53, 54, 55, 59                           |

|---------------------------------------------------------------------------------------------------------------------|

| Merck & Cie v. Gnosis S.P.A.,<br>820 F.3d 432 (Fed. Cir. 2016)                                                      |

| PersonalWeb Techs. LLC v. Apple, Inc.,         848 F.3d 987 (Fed. Cir. 2017)                                        |

| Plantronics, Inc. v. Aliph, Inc.,<br>724 F.3d 1343 (Fed. Cir. 2013)                                                 |

| PPC Broadband, Inc. v. Corning Optical Communs. RF, LLC,<br>815 F.3d 747 (Fed. Cir. 2016)27                         |

| PPC Broadband, Inc. v. Iancu, No. 2017-1362, -1363, and -1364, 2018 U.S. App. LEXIS 18297 (Fed. Cir. 2018)          |

| Rambus Inc. v. Rea,<br>731 F.3d 1248 (Fed. Cir. 2013)                                                               |

| Research In Motion Corp. v. MobileMedia Ideas LLC,<br>IPR2013-00016 (P.T.A.B. Apr. 2, 2013)31                       |

| Ryder v. United States,<br>515 U.S. 177 (1995)59                                                                    |

| SAS Institute Inc. v. Iancu,<br>138 S. Ct. 1348 (2018)                                                              |

| Sirona Dental Sys. GmbH v. Institut Straumann AG,<br>No. 17-1341, 2018 U.S. App. LEXIS 16530 (Fed. Cir. 2018)27, 29 |

| United States v. Germaine,<br>99 U.S. 508 (1879)                                                                    |

| Wasica Fin. GmbH v. Cont'l Auto. Sys., Inc.,<br>853 F.3d 1272 (Fed. Cir. 2017)32, 47                                |

(9 of 158)

# Statutes

| 35 U.S.C § 3(b)(6)        | 55     |

|---------------------------|--------|

| 35 U.S.C § 6              | 55, 56 |

| 35 U.S.C. § 3             | 58     |

| 35 U.S.C. § 3(c)          | 56     |

| 35 U.S.C. § 311           | 29     |

| 35 U.S.C. § 312(a)(3)     | 30     |

| 35 U.S.C. § 313           | 30     |

| 35 U.S.C. §§ 141(a)       | 57     |

| 35 U.S.C. §§ 311(a)       | 52     |

| 35 U.S.C. 102             | 30     |

| 35 U.S.C. 103             | 30     |

| 37 C.F.R. § 42.71(d)(2)   | 58     |

| 37 C.F.R. §§ 42.104(b)(2) | 30     |

| 5 U.S.C. § 706(2)(B)      | 59     |

| 5 U.S.C. §§ 7521          | 56     |

-

Case: 18-1768 Document: 22 Page: 9 Filed: 07/10/2018 (10 of 158)

#### STATEMENT OF RELATED CASES

No appeal from this Inter Partes Review ("IPR") has previously been before this Court or any other court.

The Court has identified *sua sponte* the following appeals as companion cases to this appeal, to be assigned to the same merits panel and argued on the same day as the present appeal:

- Kingston Technology Company, Inc. v. Polaris Innovations Limited, No. 18-1778 (Fed. Cir.)

- Polaris Innovations Limited v. Kingston Technology Company, Inc., No. 18-1831 (Fed. Cir.).

The following pending action will be directly affected by this Court's decision in this appeal: *Polaris Innovations Limited* v. *Kingston Technology Company, Inc.*, 8:16-cv-300 (C.D. Cal.). That case is currently stayed pending resolution of IPR proceedings, including among others the IPR that is the subject of this appeal and the IPRs that are the subject of the two companion cases listed above.

Case: 18-1768 Document: 22 Page: 10 Filed: 07/10/2018 (11 of 158)

#### I. STATEMENT OF JURISDICTION

The Patent Trial and Appeal Board ("PTAB" or "Board") of the United States Patent and Trademark Office ("USPTO") issued its Final Written Decision in the *Inter Partes* Review ("IPR") under 35 U.S.C. § 318(a) on January 29, 2018. Appx1-44. Polaris filed a timely notice of appeal under 35 U.S.C. §§ 141(c), 142 and 319 on April 2, 2018. Appx514-519. This Court has jurisdiction under 35 U.S.C. § 141(c) and 28 U.S.C. § 1295(a)(4)(A). The decision appealed from is final.

#### II. STATEMENT OF THE ISSUES

Whether the Board's opinion that Claims 1–17 of the U.S. Patent No. 6,438,057 ("057 Patent") are obvious should be reversed or vacated where:

- 1. The Board erred by adopting an unreasonably broad, implicit construction of the "signal indicative of [a] temperature of the DRAM array" limitation found in all challenged claims;

- 2. The Board erred by crafting, in its decision on institution of review, a new ground of unpatentability not identified in the Petition to find Claims 2, 4, 10–11, 14–15, and 17 ("the diode claims") obvious;

- 3. The Board erred by basing its unpatentability determination on factual findings unsupported by substantial evidence for all challenged claims; and

- 4. The cancellation of Polaris's claims violated the Appointments Clause of the Constitution as a final agency decision requiring the Board to act as "principal

Case: 18-1768 Document: 22 Page: 11 Filed: 07/10/2018 (12 of 158)

Officers" without having been appointed by the President and confirmed by the Senate.

#### III. STATEMENT OF THE CASE AND FACTS

#### A. Introduction

Polaris appeals the Board's Final Written Decision (Appx1-44) in the IPR that all seventeen challenged claims of Polaris's 057 patent are unpatentable. In this IPR proceeding, the Board's conclusion that Polaris's patent claims should be cancelled rests on a foundation of erroneous implicit claim construction; grounds of institution that were lacking from the petition, created by the Board, and only addressed on the merits by Kingston after all substantive written submissions from Polaris had been spent; and factual determinations on the merits that were not based on substantial evidence. Each of these errors must be corrected on appeal. Further, even holding these errors to one side, the IPR decision cancelling Polaris's patent rights was a violation of the Appointments Clause of the United States Constitution because it requires the Board to act as principal Officers even though they were never appointed by the President, by and with the advice and consent of the Senate. This Court should restore Polaris's rights.

#### B. The 057 Patent

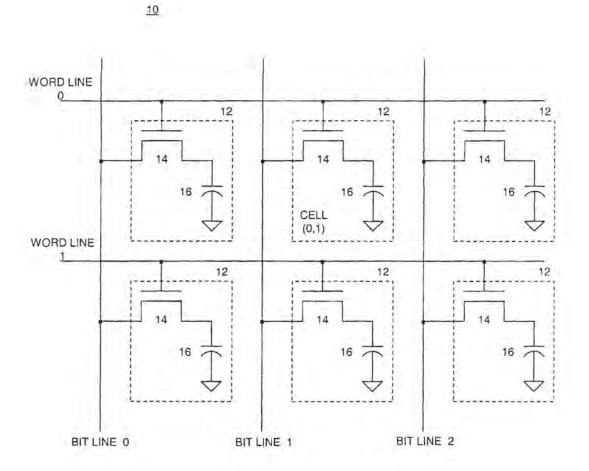

The 057 patent is directed to improvements in dynamic random access memory, or DRAM. Appx598 (1:5-10). DRAM uses stored voltages to store data

bits in arrays. Appx598 (1:46-51). DRAM is the universally dominant form of computer main memory because of its low cost due to its simple structure and dramatically lower number of components than alternatives. Appx1094 (¶ 43). But the unique, low-cost structure that gives DRAM its advantage, has attendant disadvantages, which have given rise to a long-felt need for ways to alleviate them. Appx598 (1:63-2:2); Appx1088-1089 (J 36); Appx1094 (J 43). A critical disadvantage of DRAM is that the data bits stored on its array are not permanent. Appx54. "Leakage" from its relatively simple, inexpensive arrays of storage circuits, means the stored bits only last a few microseconds and are then lost or corrupted unless their voltage is "refreshed," i.e., rewritten periodically. Appx598 (1:51-59); Appx1088-1089 (¶ 36). This refresh process may be implemented internally, as "self refresh," where "the DRAM itself set the refresh timing," or externally, where for example, an external chipset issues a refresh command to the DRAM array via a connection pin. Appx598 (1:63-2:2); Appx1088-1089 (¶ 36).

The need for continual refresh creates continual power dissipation, with attendant difficulties of temperature increase and reduced efficiency. Appx598 (2:4-14); Appx1090 (¶ 38). Because a refresh cycle includes discharging and then recharging every cell in the DRAM device, the power dissipation associated with that step is proportional to the refresh rate. Appx1088 (¶ 36).

Case: 18-1768 Document: 22 Page: 13 Filed: 07/10/2018 (14 of 158)

Furthermore, because refresh is necessary to avoid loss of stored data, it can take priority over routine reading and writing cycles, and therefore can seriously reduce "the bandwidth (e.g., data throughput) of the overall system in which the DRAM array [] is utilized." Appx598 (2:15-20); Appx1088-1089 (¶ 36). The more often the DRAM is occupied with refresh cycles, the less data throughput is available between the DRAM memory and the system utilizing it. *Id.*; Appx599 (3:58-60).

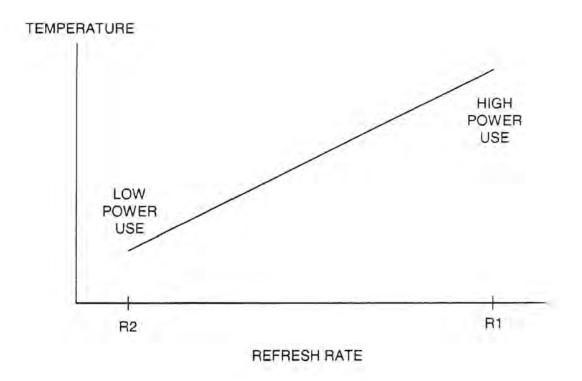

The rate of refresh necessary to reliably preserve stored data in DRAM varies with the temperature, so "when the temperature of the DRAM array is relatively high, a correspondingly high refresh rate . . . may be required to ensure integrity of the data stored in the DRAM array." Appx599 (3:55-58).

The 057 patent's inventor recognized that a significant source of DRAM's disadvantages was that conventional DRAM arrays used a high refresh rate, "based on a worst-case high temperature condition," to guard against data loss by compensating for the dependence of the necessary refresh rate on the array temperature. Appx598 (1:59-62); Appx599 (3:52-66); Appx1089-1090 (¶ 37). The inventor realized that if the temperature of the DRAM array is known to be lower than that worst-case value, a correspondingly lower refresh rate may be utilized that will ensure data integrity with lower power, higher overall system bandwidth, and more performance. Appx599 (3:60-66); Appx1089-1091 (¶¶ 37-39).

Case: 18-1768 Document: 22 Page: 14 Filed: 07/10/2018 (15 of 158)

To exploit the temperature dependence of the required refresh rate to reduce power consumption and increase performance in an acceptable tradeoff with added components and complexity, the 057 patent discloses a novel invention.

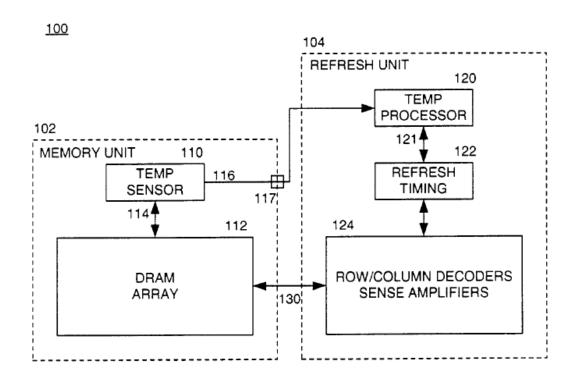

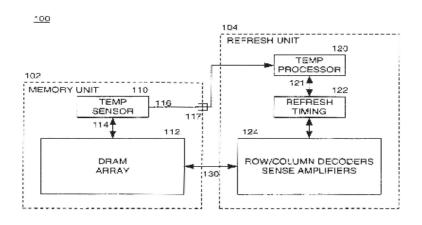

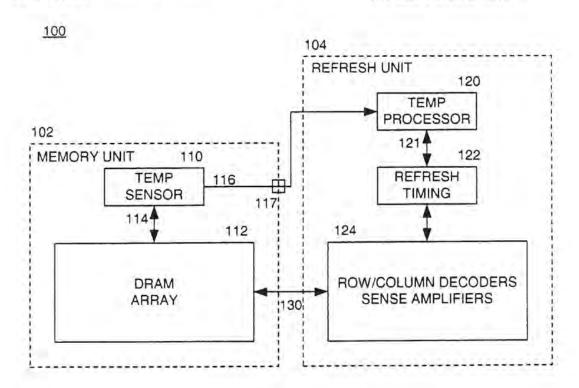

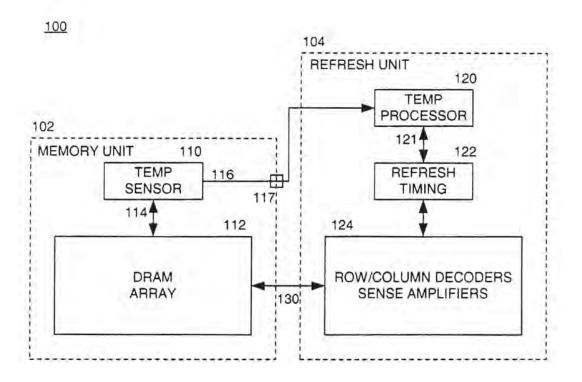

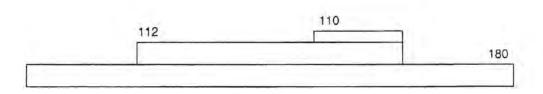

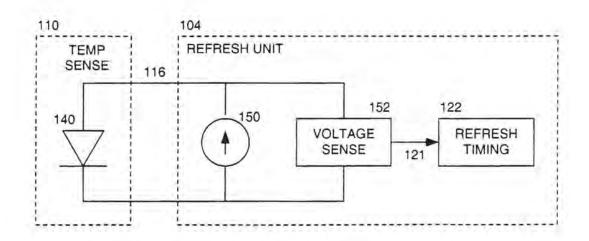

FIG. 3

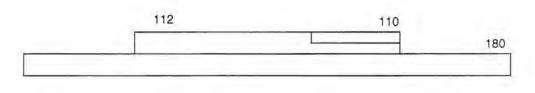

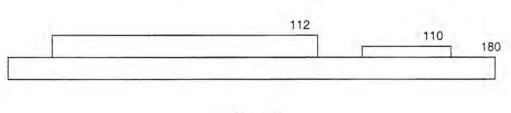

As shown in Figure 3 (Appx595), the 057 patent describes, *e.g.*, a semiconductor package (102) including at least one connection pin (117); a DRAM array (112) disposed within the package (102); and a temperature sensor (110) in thermal communication with the array (112), which is operable to produce a signal indicative of the array's temperature (116), and is coupled to the pin (117) such that the signal may be provided to external circuitry (e.g., 104), wherein the array (112)

(16 of 158)

is refreshed at a rate that decreases and increases as the temperature of the array decreases and increases, respectively. *Id.*, Appx598-600 (1:66-2:2, 2:26-37, 2:63-67, 4:18-22, 4:30-37, 4:48-53, 5:37-48, 5:60-6:7). The sensor (110) may include a diode having a forward voltage drop that varies as a function of the array's temperature so the signal corresponds to the voltage drop. *Id.*; Appx598; Appx600 (2:38-42, 2:59-62, 6:8-12); Appx1119-1120 (¶ 102).

The 057 patent allows a lower DRAM array refresh rate to be utilized during normal operation while ensuring data integrity, with the rate being increased when the temperature of the array is sensed to have increased, and decreased when the temperature of the array is sensed to have decreased, and yet does not require corresponding adjustment of the refresh rate to be implemented internally. Appx1093-1094 (¶ 42).

Because the temperature sensor and the DRAM array are disposed in a semiconductor package including at least one connection pin operable to provide the signal indicative of the temperature of the array to external circuitry, the refresh function may be performed by external circuitry during operation of the overall system. Appx599 (4:48-57); Appx1091-1093 (¶¶ 40-41).

The claimed invention not only helped meet a long-felt need to alleviate the power dissipation and efficiency disadvantages of DRAM, it achieved unexpected

Case: 18-1768 Document: 22 Page: 16 Filed: 07/10/2018 (17 of 158)

results, including one unexpected even to the inventor. Appx599 (3:64-4:10); Appx1110-1111 (¶ 82); Appx1288-1289 (165:11-166:11).

First, the claimed invention can react to an increase in the operating temperature of the array by taking actions (*i.e.*, increasing the refresh rate) that increase the temperature and increase the rate of energy consumption of the array and associated circuitry, and the thermal stress on the DRAM most when the array is at its hottest. Appx598 (1:19-21 and 2:3-12); Appx599 (3:58-4:10); Appx1093-1094 (¶ 42). Although this is a counterintuitive strategy for reducing overall array power consumption while maintaining reliability, a core principle of the invention is that it increases overall efficiency, by permitting a relatively lower refresh rate overall during operation under moderate temperatures, because it can permit a lower overall DRAM refresh rate during less active cycles compared to the relatively high conventional manufacturer-established, worst-case refresh rate. *Id.*; Appx598 (2:3-15); Appx599 (3:52-66); Appx1093-1094 (¶ 42).

Second, in DRAM technology the 057 patent's very goal—improving performance and power efficiency simultaneously—itself is nonobvious. Appx598 (2:3-24); Appx1094-1095 (¶ 44). As Kingston's expert admitted, in DRAM "if you are trying to improve performance, it's usually at the cost of energy all else being equal." Appx1203 (229:20-25); Appx1094-1095 (¶ 44). Yet the 057 patent explicitly

Case: 18-1768 Document: 22 Page: 17 Filed: 07/10/2018 (18 of 158)

stated—and accomplished—the goal of doing both simultaneously. Appx598 (2:3-24).

Third, the invention provided synergy within the framework of the very rapid paradigm shift in the computer industry from asynchronous to synchronous system memory that occurred soon after the invention. Appx1095-1096 (¶ 45); Appx1110-1111 (¶ 82); Appx1161 (59:13-17); Appx1162 (62:5-8); Appx1275 (112:8-113:11). A characteristic of the paradigm shift to "synchronous" DRAM ("SDRAM"), and now DDR (Double Data Rate), dominating the DRAM market, is that the DRAM's operation, including its refresh cycles, may be controlled according to the *external* system clock, making the refresh, from the system's perspective, deterministic, and permitting the system to both adjust refresh rates to keep them only as high as needed and coordinate that refresh rate with external data traffic needs of transferring data to the memory blocks. Appx1095-1096 (¶ 45)

Prior to SDRAM paradigm shift, normal (non-synchronous) DRAM was limited in its access time by its internal wiring and transistor speeds. Appx1096 (¶ 47). As integrated circuit technology progressed, internal circuit speeds now far exceed external communication speeds and the industry has found that the clock speed in the DRAM should be better controlled from outside the chip, to let the board or system designer provide the fastest possible external circuits and synchronize the

Case: 18-1768 Document: 22 Page: 18 Filed: 07/10/2018 (19 of 158)

external bus with each DRAM since the board signal delays now dominate data transfer to the chips. *Id.* (¶¶ 46-47)

Hence, it is now found that synchronization is best handled off the chip. *Id*. Before SDRAM took the industry by storm, it would not have been obvious to add an external pin to facilitate such synchronization because of the increased complexity of placement and routing, nor would it have been obvious to place (as in the 057) an onboard sensor to generate a temperature indicative signal for external provision. *Id*.; Appx1096-1097 (¶ 48).

One particular opportune result of this paradigm shift, however, is that SDRAM that uses the claimed invention synergistically improves both the memory's effective performance, and in the 057 patent's terms its bandwidth, by externally controlling the timing of the refresh to coordinate it with read and write cycles based on the interactively monitored needs of the chips and adjustment during operation based on the internal temperature of the DRAM array. Appx1094-1096 (¶¶ 44-45); Appx1275 (112:8-23).

#### C. The *Inter Partes* Review

Appellee Kingston filed an IPR petition seeking review of Claims 1–17 of the 057 patent. Appx45-115. Kingston challenged all claims as obvious on the following four grounds:

Case: 18-1768 Document: 22 Page: 19 Filed: 07/10/2018 (20 of 158)

| Ground 1: | § 103 in view of Atkinson       | Renders claims 1-17 obvious for |

|-----------|---------------------------------|---------------------------------|

| Ground 1: |                                 | § 103(a)                        |

| Ground 2: | § 103 in view of Atkinson and   | Renders claims 1-17 obvious for |

|           |                                 |                                 |

|           | Broadwater                      | § 103(a)                        |

| G 10      | §103 in view of Tillinghast and | Renders claims 1-17 obvious for |

| Ground 3  | Broadwater                      | § 103(a)                        |

|           | §103 in view of Kodama and      | Renders claims 1-17 obvious for |

| Ground 4  | Lee '970 or Broadwater          | § 103(a)                        |

See Appx60-61. Kingston also included a list of prior art references, which included references cited in the four grounds ("Atkinson," "Broadwater," "Tillinghast," "Kodama," and "Lee '970") and two additional references, "JPS499" and the "Kagenishi paper." Appx61-62. More importantly, Kingston did not identify Miller (U.S. Patent No. 3,812,717) or Suzuki (U.S. Patent No. 6,134,667) anywhere in the Proposed Grounds of Unpatentability. Appx60-62.

(21 of 158)

With respect to Ground 1 based on Atkinson, the Petition referred to Miller only once as an example of the supposed evidence of the finite number of alternatives.<sup>1</sup> Appx71. Ground 2 made no mention of Miller at all.

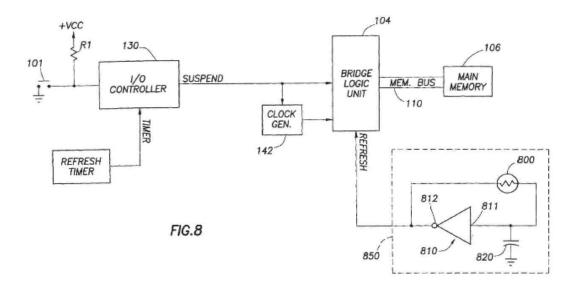

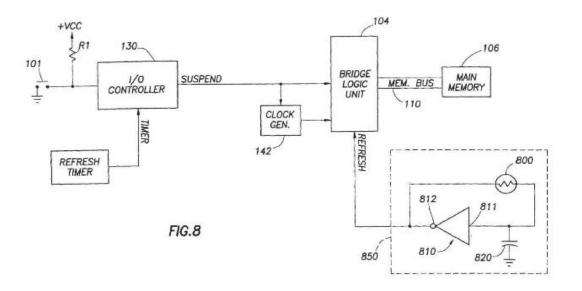

Atkinson is devoted to self-refresh of DRAM during sleep mode. In normal, active, operational mode, when data is constantly read and written to the memory, there is no motivation to have a "slow" refresh circuit that is controlled internally. Appx1098 ( $\P$  51-53). When the overall system is in "suspended operation," however, the circuitry external to the DRAM is sleeping and frozen, and the system clock is off. Appx891 (6:5-11); Appx895 (14:10-31); Appx900 (23:43-46, 24:22-28, 24:40-44); Appx1098 (¶¶ 51-53). Atkinson is designed to maintain the refresh clock of the DRAM internally, for "self-refreshing" "during suspended operation." Appx900 (24:22-28); Appx1269 (87:23-88:18). Every embodiment of Atkinson is directed to "self-refreshing" during such suspended operation, when the system clock is off and the system is frozen. Id. Atkinson prefers to rely on empirical analyses of the typical rate of cooling of DRAM when the system is in sleep mode. Id.; Appx891-892 (6:30-46, 6:63-7:19, 7:20-31). In a few non-preferred embodiments, Atkinson has a temperature sensor onboard the DRAM. Id.; see also

<sup>&</sup>lt;sup>1</sup> The IPR petition references Miller only five times, and the first two are typographical errors. *See* Appx69 (twice, but quoting from Ex. 1014, which is Suzuki, not Miller); Appx71; Appx91; Appx105. Polaris raised this error, Appx236, but the Board continued to rely on Miller, not Suzuki.

(22 of 158)

Appx892 (7:32-53); Appx898 (20:64-67); Appx899 (22:39-41); Appx900 (23:30-43). But even then, as the Petition admits, Atkinson does not provide signals indicative of the array temperature to external circuitry via a connection pin. Appx68. Nor could it: when Atkinson's invention is operating, everything else in the system is shut off, and there is nothing to which to communicate this information. Appx1099-1100 (¶ 55).

Kingston argued that Atkinson is directed to reducing battery drain and varying refresh according to temperature. Appx688 (¶ 38). But Atkinson is directed to these goals during suspended operation only. Appx895 (13:11-18) ("During low power modes, the present invention advantageously refreshes memory at a slower rate than during normal operation."); Appx900 (23:43-46, 23:65-67, 24:40-47); Appx1098 (¶ 51-52). Unlike the 057 patent, Appx598 (2:32-34), Atkinson does not permit reducing the default rate of DRAM refresh during operation. Instead, Atkinson takes the default operational rate of refresh as a given (or "reference" rate), and proposes a technique for saving energy only during *non*-operation by cutting the rate of refresh below the high default operational level. *Id.* Appx891 (6:5-11, 6:14-26); Appx1098-1099 (¶ 54).

Thus, Atkinson is intended to operate only in low-temperature shutdown situations when the chips are expected to be cooler than normal operating temperature—and indeed when they would be expected to involve two or three

(23 of 158)

orders of magnitude less power dissipation than normal operation. Appx1092-1093 (¶ 41); Appx1098-1099 (¶ 54); Appx1109-1110 (¶¶ 80-81).

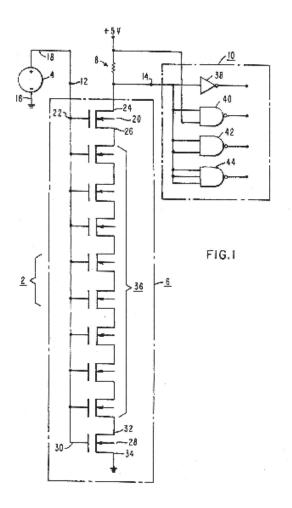

Broadwater, by contrast, is directed to detecting and reducing the effects of thermal stress on packaged semiconductor chips "such as . . . the control systems of high-speed aircraft" to promote their continued reliable operation by preventing an excess rise in temperature. Appx741 (1:25-29, 1:46-51); Appx30; Appx1100 (¶ 56). Broadwater makes no mention of memory, DRAM, or DRAM refresh. Unlike the 057 patent's DRAM refresh invention, which responds to increasing temperature in the DRAM array by increasing the refresh rate to prevent data loss, and therefore increasing circuit activity and heat dissipation in the array (see, e.g., Appx598 (1:51-59); Appx1106 (¶ 73)), Broadwater responds to increased temperature in its circuitry by shutting circuitry down to reduce temperature increase from the circuits' activity. Appx741 (1:14-45); Appx742 (3:48-64); Appx743 (5:21-27); Appx1100-1101 (¶ 57); Appx1106 (¶¶ 71, 73); Appx1280 (133:1-8). Kingston proposed to combine Atkinson with Broadwater for only one purpose: adding Broadwater's connection pin for provision of a temperature-related signal to external circuitry. Appx80.

Polaris filed a Preliminary Response, pointing out reasons why each ground Kingston identified in the Petition was deficient. Appx116-178.

The Board granted review based on only one of the four grounds identified in the Petition. Kingston's second ground sought review of Claims 1-17 based on

(24 of 158)

obviousness over "Atkinson and Broadwater." The Board instituted review on that ground of Claims 1, 3, 5-9, 12, 13, and 16 only. Appx199. The Board instituted review of the remaining challenged Claims 2, 4, 10, 11, 14, 15, and 17 (the "diode claims," requiring "at least one diode having a forward voltage drop that varies as a function of the temperature of the DRAM array" and corresponding signal), the Board formulated a *sua sponte* ground: Atkinson, Broadwater *and Miller*. *Id*. Rather than grapple with the deficient way in which Miller had been used as supposed evidence of the finite number of alternatives, the Board reasoned that the Petition "relied" on Miller in the analysis of these claims, and decided to "therefore, treat Petitioner's analysis of Claims 2, 4, 10, 11, 14, 15, and 17 based upon Atkinson, Broadwater, and Miller from the statement as a separate ground of patentability," with Miller included as a third member of the alleged obviousness combination. Appx183 n.4. The Board rejected Polaris's argument in the preliminary response that there was no motivation to combine Miller—without, however, identifying any such alleged motivation. Thus, the Board instituted review on all challenged claims follows: as

| References                       | Basis    | Challenged Claims            |

|----------------------------------|----------|------------------------------|

| Atkinson and Broadwater          | § 103(a) | 1, 3, 5–9, 12, 13, and 16    |

| Atkinson, Broadwater, and Miller | § 103(a) | 2, 4, 10, 11, 14, 15, and 17 |

Case: 18-1768 Document: 22 Page: 24 Filed: 07/10/2018 (25 of 158)

### Appx199.2

Polaris then filed its Response to the Petition, rebutting the instituted grounds. Appx210-279. Polaris challenged the Board's sua sponte ground based on "Atkinson, Broadwater, and Miller," because it, among other things, deprived Polaris of the right to file a preliminary response identifying reasons why that theory failed to meet the requirements of the statute. Appx236-245. Polaris also submitted argument, supported by direct and cross-examination testimony and documentary evidence, rebutting the two instituted grounds on the merits. Appx245-277. For example, Polaris showed that Atkinson, which is active only in a computer laptop's sleep mode, contains no teaching of "reducing the effects of thermal stress on the DRAM." Appx264. Polaris also demonstrated at least three objective indicia of nonobviousness: the long-felt need to alleviate DRAM's deleterious effects on energy efficiency and increased heat dissipation (Appx221); the unexpected result of alleviating both at the same time by adding to the DRAM's cost and complexity (Appx225-226); and the unexpected and synergistic result that the invention made possible of external synchronization of refresh rates with other signaling in SDRAM based on the actual temperature of the DRAM array (Appx227).

<sup>&</sup>lt;sup>2</sup> The Board's denial of institution on the other proposed grounds (*i.e.*, Grounds 3 and 4) is not before the Court. The Board instituted review on every challenged claim. *See SAS Institute Inc. v. Iancu*, 138 S. Ct. 1348 (2018). That determination was neither challenged before the Board nor appealed.

(26 of 158)

With its Reply, Kingston attached no evidence except for the transcript of the deposition of Polaris's expert. Appx280-309. Kingston raised, however, a host of new issues and arguments, that changed the issues and unpatentability rationales that had been raised in the Petition. For example, Kingston argued that the ordinary artisan would have been motivated to combine Atkinson and Broadwater to give Atkinson, a reference that operates only in sleep mode, "overheat protection" as a "safety measure," even though Atkinson has no teachings regarding overheating risk, has no external circuitry to monitor such risk, offers power dissipation in orders of magnitude well below the normal operation during the sleep mode, and shuts off all circuitry to take advantage of the low temperature in sleep mode to reduce the self-refresh rate for increased power efficiency. Appx285-286; Appx286-288; Appx295-296. Kingston also now argued that all "temperature sensors" were *inherently* "operable to produce a signal indicative of a temperature" that "may be provided to external circuitry" via a connection pin as the claims require—in other words, for the first time effectively reading the latter limitations out of the claims for the first time. Appx288-289.

Polaris asked the Board for a conference to request relief in light of the improper Reply arguments. Appx1421-1423. The Board denied Polaris's request for a conference, but allowed Polaris to file a short, non-argumentative list of new issues in the Reply. *Id*. In its rebuttal, Kingston did not argue that any of the new arguments

(27 of 158)

were actually in the petition, only that they were "supported" by the Petition. Appx318-322.

The Board then issued a Final Written Decision finding all challenged claims unpatentable. Appx43. The Board stated that none of the arguments or issues in Kingston's Reply was untimely, Appx17-18 n.6, and relied mainly on Kingston's arguments, without its own separate factual findings. See, e.g., Appx13-17; Appx22-30; Appx32-37; Appx40; Appx42. The Board found that Atkinson taught or suggested the limitation of producing a signal indicative of a temperature of the DRAM array that may be provided to external circuitry over the connection pin. Appx14-15. The Board did not identify where this signal was produced in Atkinson, but concluded that it would have been obvious for an ordinary artisan to add it. Appx15-16. The Board found that Atkinson's teachings included "preventing [] overheating" and that it taught that it could overheat while in sleep mode. Appx22; Appx25. The Board refused to give any weight to Polaris's objective indicia, contending that the unexpected synergy with external synchronization was not entitled to weight because it was "not recite[d]" in the claim, and ignoring the other two indicia. Appx23.

With respect to the diode claims, the Board relied solely on its *sua sponte* ground including Miller to find unpatentability. Appx32; Appx42. The Board found that the motivation to add Miller's diode to Atkinson was "to enable the use of

(28 of 158)

Atkinson's DRAM in a 'cooling regime'," "to enable throttling of power to reduce heat," and to reduce "thermal stress in the DRAM." Appx35. But the Board's reason of "cooling regime" for combining Miller with Atkinson is not found in Miller although both Kingston and Kingston's expert suggested that it is. Appx69; Appx692-693. Miller does not discuss a "cooling regime" or any form of cooling. Appx966-972. Instead, it is Suzuki that mentions cooling control. Appx930. The Board's purported motivation to combine Miller and Atkinson and Broadwater thus relies in part on a motivation that is not found in any of the three references in the alleged combination, but a fourth reference the Board never added to the combination. Also, the Board ignored Polaris's evidence that adding Miller's diode to Atkinson's DRAM module would increase, not decrease, its continual power dissipation. *Compare* Appx33 with Appx 34-36.

#### IV. SUMMARY OF ARGUMENT

The Board's decision cancelling Polaris's patent claims was based on three critical errors, each one of which makes the decision unsustainable on appeal. It was based on an overbroad, implicit claim construction that negates the literal language of the claims. It was based on a new obviousness combination that was created by the Board in contravention of the Supreme Court's recent precedent. And it was based on factual determinations that cannot survive substantial evidence review.

(29 of 158)

First, the Board erred by implicitly nullifying the claim term "signal indicative of [a] temperature of the DRAM array," which the 057 patent requires to be capable of being output to an external circuitry so that it can cause the refresh rate from the external circuitry to change. According to the Board's obviousness determination, this internal signal that can be output to cause external changes to a refresh rate would be met by an internal refresh signal that cannot be output to indicate temperature. The Board's sub silentio construction thus nullifies the key distinction between the temperature signal and the phenomena it is meant to influence, as well as the key distinction between internal and external refresh control.

Second, the Board acted beyond its statutory authority when it instituted the IPR and cancelled Polaris's diode claims based on a ground that was not presented in the Petition. Here, the Board took critically deficient obvious-to-try evidence from a single-reference obviousness ground that was in the Petition and used it to craft a new three-reference obviousness combination that was not in the Petition. The Supreme Court's recent SAS decision laid to rest any doubt that the Board is allowed to institute an IPR or cancel claims on an unpetitioned ground and the Board's decision accordingly cannot stand. Moreover, even if considered on its merits, the PTAB's new ground cannot be sustained as it lacks substantial evidence; instead, it would render the primary reference, Atkinson, inoperable for its intended purpose.

(30 of 158)

Third, on the claims that do not specifically include diode limitations ("non-diode claims"), the Board erred by basing its unpatentability determination on findings unsupported by substantial evidence. The Board's purported motivation to combine Atkinson and Broadwater is based upon its determination that both Atkinson and Broadwater teach prevention against overheating. However, Atkinson has no such concern and in fact is directed exclusively to low-heat states, orders of magnitude cooler than ordinary—let alone overheated—operation. Further, the Board's decision lacks substantial evidence supporting the key portion of its obviousness analysis, namely, that Atkinson would have incorporated Broadwater's pin to maximize power saving. The Board also erred by not considering the impact of three objective indicia of nonobviousness.

Finally, the Board's decision must be set aside as a violation of the Appointments Clause of the United States Constitution because the PTAB judges, exercising significant authority pursuant to the laws of the United States, acted to terminate Polaris's patent rights even though they were never appointed by the President and never confirmed by the Senate.

#### V. ARGUMENT

#### A. Legal Standards

This Court reviews the Board's claim construction and ultimate determinations of obviousness *de novo* and the underlying factual findings for

(31 of 158)

substantial evidence. *Ariosa Diagnostics v. Verinata Health, Inc.*, 805 F.3d 1359, 1364 (Fed. Cir. 2015); *Lighting Ballast Control LLC v. Philips Elecs. N. Am. Corp.*, 744 F. 3d 1272, 1276-1277 (Fed. Cir. 2014) (en banc). Whether a ground the Board relied upon was new is a question of law subject to *de novo* review. *In re NuVasive, Inc.*, 841 F.3d 966, 970 (Fed. Cir. 2016). The "substantial evidence" standard "requir[es] a court to ask whether 'a reasonable mind might accept' a particular evidentiary record as 'adequate to support a conclusion." *Dickinson v. Zurko*, 527 U.S. 150, 162 (1999).

B. The Board Applied An Overbroad Interpretation Of "Signal Indicative Of The Temperature Of The DRAM Array" To Include Signals Not Outputtable To External Circuitry Via A Connection Pin

In its Final Written Decision, the PTAB improperly adopted an overbroad implicit construction of the recited "temperature sensor in thermal communication with the DRAM array, operable to produce a *signal indicative of a temperature of the DRAM array*, and coupled to the at least one *connection pin such that the signal may be provided to external circuitry*" that the Board erroneously used to find this limitation disclosed in Atkinson. The plain language of the claim requires the "signal indicative of a temperature of the DRAM array" to be *the same* "signal that may be

<sup>&</sup>lt;sup>3</sup> All emphases throughout Polaris's principal brief are added unless stated otherwise.

(32 of 158)

provided to external circuitry." But that is not the understanding the Board applied. The Board instead relied upon a refresh signal in prior art (Atkinson) as both a refresh signal and a temperature indicative signal, although they are claimed as separate signals, and the refresh signal in the prior art is not outputtable to external circuitry.

The Petition disavowed any need for claim construction. Appx62. Because Kingston offered no express constructions of the claims, Polaris had no burden to be the first to propose any constructions. The Final Written Decision likewise declined to adopt any express constructions. Appx7 ("We determine that it is not necessary to provide any express interpretation of the claim terms."). Nevertheless, as this Court has explained, "[d]espite no express construction of [the term] below, Board findings establishing the scope of the patented subject matter may fall within the ambit of claim construction. Because [Petitioner]'s challenge is directed to the Board's expression of its understanding of the scope of the claim term . . . , it is properly before us on appeal." *HTC Corp. v. Cellular Comm'ns Equipment, LLC*, 877 F.3d 1361, 1367 (Fed. Cir. 2017).

The Board's Final Written Decision found that Atkinson discloses a temperature sensor operable to produce a signal that may be provided to external

(33 of 158)

circuitry via a connection pin.<sup>4</sup> Appx14-15. But the Board nowhere identified a "signal indicative of a temperature" that is also *the same* signal that may be provided to external circuitry via a connection pin as claimed even though the claim language requires precisely that. Instead, the Board merely pointed to circuitry on Atkinson's DRAM module that generates a pulse that acts to refresh the DRAM. Appx15.

In identifying what it perceived as "[a]n example of a suitable temperature sensor," the Board relied upon Atkinson's "alternate embodiment" (Appx67) where a temperature sensor on the DRAM memory module itself provides a "voltage" to a voltage controlled oscillator ("VCO") "that represents the main memory temperature," causing the VCO to produce a "refresh signal" that refreshes the DRAM array. Appx14. But both the intrinsic and extrinsic evidence are contrary to the Board's broad and incorrect understanding of claim scope, which would make a refresh signal be the temperature-indicative signal that may be output to external circuitry. The claims, however, recite the "signal indicative of the temperature" that may be provided "to external circuitry," external to the DRAM array, and separately recite the refreshing of the DRAM array itself. Claim 13, for example, separately recites "a signal indicative of a temperature of the DRAM array" that may be

-

<sup>&</sup>lt;sup>4</sup> Some of the claims' language relating to these limitations differs from one another, *e.g.*, *compare* Claim 1 *with* Claim 16, but the Final Written Decision addresses all seventeen claims in the same manner with respect to this limitation.

(34 of 158)

"provide[d] . . . to external circuitry" via a "connection pin;" and "refresh[ing] the DRAM array at a rate that varies in response to the signal." Appx600-601. The specification also confirms that the claimed temperature-indicative signal that may be provided to external circuitry via a pin is not the same as the signal that refreshes the DRAM (e.g., the signal 116 indicative of a temperature of the DRAM array 112 is not the same as the refresh signal 130 as shown in Fig. 3 above). Appx595; Appx599 (4:17-21, 4:30-32). The Final Written Decision itself also acknowledges the 057 patent's description of "signal 116 from temperature sensor 110 indicating a temperature sensed from DRAM array 112," and its separate description, in the same sentence, of "refresh signal 130 to refresh DRAM array 112 at a rate that varies in response to received temperature signal 116," wherein the package containing the DRAM array "includes at least one connection pin 117 operable to provide the *signal on line 116* to external circuitry, such as the refresh unit 104" that "produces refresh signal 130." Appx4-5 (quoting Appx599 at 4:30-32 and 4:49-53).

Moreover, the claim language requires that the temperature indicative signal may be outputted to an external circuitry. But Atkinson does not produce a temperature signal that can be provided via a pin to the external circuitry. As the Final Written Decision acknowledges, Kingston itself concedes that the embodiment relied upon in Atkinson "does not disclose providing the temperature signal to an external circuit," and merely contends it would have been obvious to provide such a

(35 of 158)

signal to such a circuit from the DRAM array. Appx15. But Polaris offered unrebutted expert testimony establishing that Atkinson has no active external circuitry to which to send such signals, and, moreover, could not generate a temperature indicative signal that could even be provided to the external circuitry via a connection pin without "wholesale modification of the control circuit" of Atkinson. Appx1099-1110 (¶ 55); Appx1103 (¶ 62); Appx1114 (¶ 88); Appx1278 (124:15-126:1). Therefore, Atkinson does not disclose this limitation. The Board ignored this evidence.

In a recent case, this Court reversed where the Board adopted an unreasonably broad construction of "signal" that ignored the requirement the claimed signal must meet. In *In re Hodges*, the Board found unpatentable claims reciting a "signal," where the written description made "clear . . . that the [claimed] signal must at least be capable of being compared to 'a predetermined limit," because the specification "explain[ed] that the sensor 'may transmit the signal to an indicator, such as a pressure gauge or alarm system, to provide a visual or audible indication of the operability of the drain valve,' and that a controller can 'compare[] the signal to a predetermined limit and generate[] a control signal based on this comparison'." 882 F.3d 1107, 1115 (Fed. Cir. 2018). This Court found that the Board adopted a "strained" and "unreasonably broad" interpretation of "signal" encompassing any "act, event, or the like that causes or incites some action," which "would encompass

(36 of 158)

virtually any . . . component within the valve drain that moves in response to the flow of fluid through the drain." *Id*. That interpretation was "unreasonable" because "the specification . . . state[d] that the sensor 'generates a signal,' which, in turn, can be transmitted to a pressure gauge to 'provide a visual . . . indication of the operability of the drain"—"[i]n other words," the "'movement of' the . . . gauge's needle 'in response to the sensed pressure" was not "itself" the recited "signal," according to the specification, but, rather, "the recited 'signal' causes the pressure gauge to provide a visual indication." *Id*. The prior art merely disclosed a movement of a piston, which, "[u]nder any reasonable construction of 'signal,' . . . cannot be compared to a predetermined limit, as described." *Id*.

Similarly, here, contrary to Kingston's suggestion that the claimed temperature signal may be the same as the refresh signal that pulses the DRAM in response to it, Appx303, the temperature signal that may be provided to the external circuitry cannot, in light of the intrinsic evidence, be interpreted to correspond to Atkinson's refresh pulse generator under any reasonable construction of that term.

The claimed "signal" may not be interpreted to encompass refresh signals or other signals that are not, without more, provided via a connection pin to indicate temperature. Because the Board purported to find these limitations in Atkinson and Atkinson merely generates refresh pulses that may not, without more, be provided via a connection pin to indicate temperature, and this error affects all cancelled

(37 of 158)

Claims, its decision should be vacated. See, e.g., PPC Broadband, Inc. v. Corning Optical Communs. RF, LLC, 815 F.3d 747, 756 (Fed. Cir. 2016) (vacating the Board's Final Decision because "the Board's construction is not reasonable in light of the specification"); D'Agostino v. MasterCard Int'l, Inc., 844 F.3d 945, 947 (Fed. Cir. 2016) (vacating the Board's claim constructions "[b]ecause the Board's decisions rest on an unreasonable claim interpretation.").

## C. The Board's Decision To Institute And Cancel Claims On A Ground Not Identified In The Petition Requires Reversal

The PTAB is not free to institute an IPR or invalidate claims on an unpetitioned ground. The Supreme Court has put to rest the notion that it could. *SAS*, 138 S. Ct. at 1348. And this Court has since recognized that such a deviation from the petition is not permissible under *SAS*. *Sirona Dental Sys*. *GmbH v*. *Institut Straumann AG*, No. 17-1341, 2018 U.S. App. LEXIS 16530 (Fed. Cir. 2018). That is what happened here. The Board instituted the IPR based on the three-legged obviousness combination of Atkinson, Broadwater, and Miller, against the diode claims, that was not in the petition, forcing Polaris to rebut that ground when Kingston had never made a *prima facie* showing. The Board's decision must be reversed.

### 1. The Board Cannot Institute An IPR Or Cancel Claims On An Unpetitioned Ground

(38 of 158)

The Board is not authorized to institute an IPR or cancel claims on unpetitioned grounds. In *SAS*, the Supreme Court laid to rest any notion to the contrary when discussing the PTAB's obligation in an IPR once instituted, to find on the patentability of all challenged claims. The Supreme Court explained that the statutory language:

doesn't authorize the Director to start proceedings on his own initiative. Nor does it contemplate a petition that asks the Director to initiate whatever kind of inter partes review he might choose. Instead, the statute envisions that a petitioner will seek an inter partes review of a particular kind—one guided by a petition describing "each claim challenged" and "the grounds on which the challenge to each claim is based." §312(a)(3). From the outset, we see that Congress chose to structure a process in which it's the petitioner, not the Director, who gets to define the contours of the proceeding.

SAS, 138 S. Ct. at 1355. The Supreme Court further explained:

More confirmation comes as we move to the point of institution. Here the statute says the Director must decide "whether to institute an inter partes review . . . pursuant to a petition." §314(b). The Director, we see, is given only the choice "whether" to institute an inter partes review. That language indicates a binary choice—either institute review or don't. And by using the term "pursuant to," Congress told the Director what he must say yes or no to: an inter partes review that proceeds "[i]n accordance with" or "in conformance to" the petition. OED, www.oed.com/view/Entry/155073.

*Id.* at 1355-56. The Supreme Court explained: "*Nothing* suggests the Director enjoys a license to depart from the petition and institute a *different* inter partes review of his own design." *Id.* at 1356 (second emphasis in original).

(39 of 158)

The rest of the statute confirms, too, that the petitioner's petition, not the Director's discretion, is supposed to guide the life of the litigation. For example, §316(a)(8) tells the Director to adopt regulations ensuring that, "after an inter partes review has been instituted," the patent owner will file "a response to the petition." Surely it would have made little sense for Congress to insist on a response to the petition if, in truth, the Director enjoyed the discretion to limit the claims under review. What's the point, after all, of answering claims that aren't in the proceeding?

Id (second emphasis in original). The Supreme Court thus expressly acknowledged that part of why the scope of the IPR must track the scope of the petition is *because* of the statutory right to respond to the petition itself. For these reasons, the PTAB is not free to "say yes" to a different ground than the one presented in the petition. Accordingly, this Court has explained, citing SAS, that "It would thus not be proper for the Board to deviate from the grounds in the petition and raise its own obviousness theory . . . ." Sirona, 2018 U.S. App. LEXIS 16530, at \*13.5

\_

<sup>&</sup>lt;sup>5</sup> In *Sirona*, after acknowledging that *SAS* precluded deviating from the petition, this Court rejected appellant's argument "that the Board relied on theories that first appeared in the final written decision[.]" *Sirona*, 2018 U.S. App. LEXIS 16530, at \*12. There the Board cancelled certain claims on an obviousness combination that *was* in the petition. *Id.* at \*2-3. This Court concluded that "[t]he Board did not change theories simply because the petition did not use the exact words" that the Board used to describe the same reference in the same combination. *Id.* at \*13. This Court also instructed the Board to consider on remand, under *SAS*, "whether it may consider combinations of references not argued by the petitioner in opposing [a] motion to amend claims, and, if so, what procedures consistent with the APA are required to do so," but only after first overruling the Board's decision on the same motion on other grounds. *Id.* at \*16-17. Indeed, the Court only considered that additional obviousness combinations might be permissible only in the context of a motion to amend, making clear they are not permissible otherwise. This Court in *Sirona* has

(40 of 158)

The statute is consistent. An IPR can only be initiated when "a person who is not the owner of the patent" (35 U.S.C. § 311) files a detailed petition "identif[ying] with particularity," "the grounds on which the challenge to each claim is based, and the evidence that supports the grounds for the challenge to each claim." 35 U.S.C. § 312(a)(3). The patent owner has the "right to file a preliminary response to the petition . . . that sets forth reasons why no inter partes review should be instituted based upon the failure of the petition to meet any requirement of this chapter." 35 U.S.C. § 313. By regulation, the petition must identify "[t]he specific statutory grounds under 35 U.S.C. 102 or 103 on which the challenge to the claim is based and the patents or printed publications relied upon for each ground," and separately also identify "where each element of the claim is found in the prior art patents or printed publications relied upon." 37 C.F.R. §§ 42.104(b)(2), (5); see also §§ 42.108(a), (c). Instituting on unpetitioned grounds subverts **both** the requirement that the IPR only proceed on the basis of the petition, and the right of the patent owner to defeat institution on a showing a "failure of the petition."

Further, instituting an IPR or cancelling claims on unpetitioned grounds shifts the burden to the patent owner to defeat the ground before making the petitioner present a *prima facie* case. *See In re Magnum Oil Tools Int'l*, *Ltd.*, 829 F.3d 1364,

recognized the impact of SAS. Under the same reasoning in Sirona, the Board erred here.

(41 of 158)

1376 (Fed. Cir. 2016) ("We thus disagree with the PTO's position that the burden of production shifts to the patentee upon the Board's conclusion in an institution decision that 'there is a reasonable likelihood that the petitioner would prevail.""); id. at 1380-81 (rejecting "the PTO's assertion that the Board did not err in making an obviousness argument on behalf of [the petitioner] based on the primary reference Lehr because this argument 'could have been included in a properly-drafted petition[]" and explaining that "[i]t is the petitioner that bears the burden of proof in IPRs.").

It follows that if the PTAB cannot *institute* on an unpetitioned ground, the PTAB also cannot *cancel claims* on an unpetitioned ground.<sup>6</sup> Even before *SAS*, this Court had recognized that the PTAB cannot cancel claims based on new grounds:

We also are unpersuaded by [petitioner]'s attempts to cure the petition's deficiencies in its subsequent briefing to the Board and to us... Here, Continental did not make out its obviousness case in its petition .... After [patent owner] pointed out the flaws of this position, [petitioner]'s ensuing arguments to the Board and to us effectively abandoned its petition in favor of a new argument. ... Rather than explaining how its original petition was correct, [petitioner]'s subsequent arguments amount to an entirely new theory of prima facie obviousness absent from the petition. Shifting arguments in this fashion is foreclosed by statute, our precedent, and Board guidelines.

<sup>&</sup>lt;sup>6</sup> The PTAB panel has properly refused to consider arguments if they were not raised in the petition. *See*, *e.g.*, *Research In Motion Corp.* v. *MobileMedia Ideas LLC*, IPR2013-00016, Paper 19 at \*3 (P.T.A.B. Apr. 2, 2013).

(42 of 158)

Wasica Fin. GmbH v. Cont'l Auto. Sys., Inc., 853 F.3d 1272, 1286 (Fed. Cir. 2017). As this Court has explained: "It is of the *utmost importance* that petitioners in the IPR proceedings adhere to the requirement that *the initial petition* identify 'with particularity' the 'evidence that supports the grounds for the challenge to each claim." Intelligent Bio-Sys., Inc. v. Illumina Cambridge, Ltd., 821 F.3d 1359, 1369 (Fed. Cir. 2016). The PTAB cannot institute an IPR or cancel claims based on an unpetitioned ground.

## 2. The Board Impermissibly Instituted IPR And Cancelled The Diode Claims On An Unpetitioned Ground

Kingston identified ground one as obviousness based on Atkinson. In discussing that ground, Kingston relied upon Miller *not* as a combinable prior art reference but as evidence of the supposed knowledge of a person of ordinary skill in the art vis-à-vis what would have been obvious to try—citing Miller as supposed proof of the finite number of alternatives. Appx71. Relevant here, Kingston also identified a second ground of obviousness as based on Atkinson combined with Broadwater. In its discussion of that second ground, Kingston did not even mention Miller. When instituting the IPR, the Board did *not* institute the IPR against any claims based on the first ground, *i.e.*, Atkinson alone with its discussion of Miller. The Board *did* institute against certain claims based on the second ground, Atkinson combined with Broadwater. And then, the Board instituted against the *diode* claims based on a new ground that the Board created for the first time *sua sponte*—

Case: 18-1768 Document: 22 Page: 42 Filed: 07/10/2018 (43 of 158)

"Atkinson, Broadwater, and Miller"—and later cancelled those claims on that ground.

But Kingston never raised any obviousness combination based on Miller. Rather, the Board by its own admission created a "separate ground of patentability" for the diode claims, stating however that Kingston's mere reliance on Miller provided a basis to add such "separate ground." Appx183. The only reliance on Miller in the Petition (typos aside) is when it was described as an "example" of the finite options known to a skilled artisan. See, e.g., Appx71 (discussing Atkinson); Appx91; Appx105 (discussing grounds not instituted): "[t]hose of ordinary skill at the time of the filing of the 057 Patent would know that one example of the finite alternate types of integrated circuits for detecting temperature was a diode having a forward voltage drop that varies as a function of temperature," and "[t]here is nothing inventive about using this known type of temperature sensor, and it would be obvious for a person of ordinary skill to have selected a diode." Appx71-72. Solely as part of its "finite alternate type" obvious-to-try argument about the Atkinson reference, Kingston pointed to, "[f]or example, Miller from 1974" as "describ[ing] a semiconductor diode 'temperature measuring apparatus' in which '[t]he temperature reading is made by measurement of the forward voltage drop across the diode." Appx71.

(44 of 158)

The Petition's "Proposed Grounds of Unpatentability" do not mention Miller. The "Summary of Grounds of Rejection" lists "Atkinson and Broadwater," but never mentions Miller. Appx60-61. The Petition's "Prior Art Offered for the Present Unpatentability Challenges" lists seven references, including Atkinson and Broadwater—but again, not Miller. Appx61-62. Similarly, Kingston's expert lists prior art and discusses its status as prior art, but does not mention Miller. Appx685-687; Appx1175 (117:1-25). The Petition's identification of "where the prior art teaches or suggests each portion of the claim, as well as . . . why a person of ordinary skill would be motivated to modify the base reference as outlined in the relevant obviousness combinations" identifies this ground repeatedly as "Atkinson in view of Broadwater" or "Atkinson and Broadwater"-and never mentions Miller. Appx62-63; Appx80; Appx81. The Institution Decision sua sponte converted Miller to a reference in a new combination. Appx 183.

The Board expressly admitted that Kingston "omitted" the ground the Board instituted on, and confirmed that it instituted on that ground anyway. *See* Appx183 n.4 ("Although *Miller is omitted from Petitioner's summary of asserted grounds*, it is nevertheless relied upon in Petitioner's analysis of claims 2, 4, 10, 11, 14, 15, and 17. *See*, *e.g.*, Pet. 20. We, therefore, treat Petitioner's analysis of claims 2, 4, 10, 11, 14, 15, and 17 based upon Atkinson, Broadwater, and Miller from the statement as a *separate ground of unpatentability*."); Appx28-29 n.7. According to the Board,

(45 of 158)

"Petitioner's discussion of Miller within the content of the Petition *as a way to bolster* the Atkinson-Broadwater combination is tantamount to the Atkinson-Broadwater-Miller combination." Appx32. This is wrong: the Petition used Miller for a supposedly finite number of options, not in a combination; the Board used Miller to create a new combination.

The Board's argument that Kingston relied on Miller is irrelevant. The question is not whether Miller was discussed *anywhere* in the petition but whether there was a proposed ground in the petition expressly combining Miller with Atkinson and Broadwater. "Mere reliance on the same statutory basis and the same prior art references, alone, is insufficient to avoid making a new ground." *In re Leithem*, 661 F.3d 1316, 1319 (Fed. Cir. 2011).

Further proving that the Board changed grounds, when Polaris addressed Miller as an obvious-to-try argument in the preliminary response, the PTAB called that issue "moot" because of its decision to treat Miller as a combinable reference in its own right. But Kingston used Miller as part of a critically defective attempt to show obviousness to try. *See* Appx71 ("Those of ordinary skill at the time of the filing of the '057 Patent would know that *one example* of the *finite alternate types* of integrated circuits for detecting temperature was a diode having a forward voltage drop that varies as a function of temperature. Ex. 1005 at ¶ 53. *For example, Miller* from 1974 describes a semiconductor diode 'temperature measuring apparatus' in

(46 of 158)

which '[t]he temperature reading is made by measurement of the forward voltage drop across the diode.' Ex. 1015 at Abstract."). Polaris then refuted that argument in its preliminary response, as was proper. *See* Appx143 ("the number of alternative sensors usable to measure temperature is far from 'small or easily traversed,' as the caselaw requires. . . . The Petition does not provide . . . what would be the easiest proof that there is a small or easily traversed set of alternatives: a list of those alternatives."); Appx144 ("Miller is not part of any combination. No motivation is given to combine with Miller. It is therefore improper to rely on Miller for disclosure of a diode.").

The PTAB should have found that the obvious-to-try/finite-possibilities argument was legally defective. Instead, the Board ignored this defective argument, calling it "moot" in light of the decision to treat Miller as a combination reference in its own right. *See* Appx197 ("Patent Owner argues that Petitioner's reliance on 'finite alternate types of integrated circuits for detecting temperatures' is a misapplication of *KSR* because the number of available alternatives is 'far from 'small or easily traversed." . . . *This argument is moot* in light of Petitioner's alternative reliance upon Miller's diode to measure the temperature of Atkinson's DRAM. Pet. 20."). While the Board characterized this as "alternative reliance," there was no such reliance. There was only the one quote (*see* Appx71) in support of the finite possibilities argument. Thus, the Board brushed to one side the weakness of

(47 of 158)

the argument Kingston actually made in its petition, by declaring it "moot" in light of a different "alternative" ground that was not actually present in the petition—an "alternative" ground that was actually not Kingston's, but the Board's.<sup>7</sup>

Further confirming the *sua sponte* nature of the combination with Miller, the Board responded to Polaris's argument that there was no motivation to combine with Miller by stating: "Patent Owner also argues that Miller is not part of any combination and that no motivation is given by Petitioner to combine Atkinson with Miller. Prelim. Resp. 22. As discussed above, however, we interpret the ground of unpatentability as including Miller." Appx197-198. In other words, the Board did not grapple with the fact that the Petition itself did not contain a legally required element of the *prima facie* obviousness on the ground before the Board reinterpreted it *sua sponte*. Instead, the Board presumed its own conclusion that Miller was a combinable reference and, citing its own presumption, excused itself from needing an actual *reason* to combine Miller with Atkinson and Broadwater as a ground of institution.<sup>8</sup>

\_

<sup>&</sup>lt;sup>7</sup> Trading a defective obvious-to-try argument for a three-reference obviousness combination changes the *substance* of the ground. *See In re NuVasive*, 841 F.3d at 972 ("In the related, non-IPR context, we have relied on the APA's requirements to find a 'new ground' where 'the thrust of the rejection' has changed, even when the new ground involved the same prior art as earlier asserted grounds of invalidity."). <sup>8</sup> Even if it *had* grappled with the lack of motivation to combine, the Board may not add its own motivation to combine. *See Rambus Inc. v. Rea*, 731 F.3d 1248, 1256

(48 of 158)

Lastly, the Board tried to justify its decision to rely on a three-reference combination by adopting Kingston's argument that the Atkinson-Broadwater ground "builds off" the Atkinson ground that cited Miller. Appx32. This argument fails for at least two distinct reasons. *First*, this argument does not address the distinction between a finite-alternatives argument and a combination. *Second*, the Board was not free to presume that the arguments about Miller in the context of Atkinson *alone* (Ground 1) would work equally well in the context of Atkinson combined with Broadwater (Ground 2), particularly when Miller does not appear in Ground 2.

The Board's decision to institute and then cancel claims based on the threereference combination including Miller was a legal error.

### 3. The Sua Sponte Ground Lacks Substantial Supporting Evidence

The Board's *sua sponte* theory still lacks substantial supporting evidence. Neither Atkinson nor Broadwater mentions forward-biased diodes. The fact that the claimed diode is a forward-biased diode, as opposed to just a diode or any other types of diodes, is significant. Kingston's expert acknowledged that there are many types of diodes and different types of diodes have different advantages and

<sup>(</sup>Fed. Cir. 2013) ("The Board erred when it supplied its own reasons to combine . . . While the Board's findings may ultimately be correct, we will not affirm a Board rejection, like this one, which essentially provides a new motivation to combine the references.").

(49 of 158)

disadvantages. Appx1168 (89:19-20); Appx1169 (90:14-17). Polaris's expert testified that the claimed forward-biased diode specifically requires "a steady-state current to flow through a voltage drop" such that it "would be useful only during active mode" and "is appropriate ... where significant power is already being dissipated due to its active state." Appx1118-1119 (¶ 100); Appx1119-1120 (¶ 102); Appx1121 (¶ 105). Because forward-biased diodes are "important structural limitation[s]," it would be an unusual case in which they could be added simply from the common knowledge of the ordinary artisan or any other such gap-filler theory. Arendi S.A.R.L. v. Apple Inc., 832 F.3d 1355, 1363 (Fed. Cir. 2016) ("[W]e conclude that while 'common sense' can be invoked, even potentially to supply a limitation missing from the prior art, it must still be supported by evidence and a reasoned explanation" in cases "where it is an important structural limitation that is not evidently and indisputably within the common knowledge of those skilled in the art ...."). Because Kingston had not raised the purported combination of Atkinson, Broadwater, and Miller in the Petition, Kingston unsurprisingly offered no motivation to make that particular combination.

The Board offered two reasons for the purported combination, but neither is supported by substantial evidence and the Board ignored uncontradicted record evidence to the contrary. The Board argued that the ordinary artisan would have "substitut[ed] Miller's forward biased diode with [sic] Atkinson's thermistor" "to

(50 of 158)

enable the use of Atkinson's DRAM in a 'cooling regime' as well as 'to enable throttling of power to reduce heat as well as to monitor and track the memory temperature for diagnostic purposes," and to "predictably . . . reduc[e] thermal stress in the DRAM, upon being notified that the DRAM is overheating." Appx35. Not so.

First, as to the "cooling regime" motivation theory, the Board relied upon Kingston's Petition which represented that "[o]ne of ordinary skill in the art would be motivated to send the signal indicative of memory temperature to an external connection pin, at least to enable its use in a cooling regime, such as the one set forth in Miller.' Pet. 18." Appx34. But no "cooling regime" is described in Miller. Instead, despite Kingston's Petition (Appx69) and its expert's declaration (Appx692-693, ¶ 49) to the contrary, the passage Kingston relied upon, and the Board adopted, is from an entirely different reference, Suzuki, which was never discussed by the Board or Kingston. Appx140-141; Appx236 n.3; Appx951 (1:62-65). Therefore, the record before this Court does not identify what a combination of Atkinson-Broadwater-Miller-Suzuki would look like. Next, Kingston's argument about the "cooling regime" was not related to any diode claim, but to a limitation in the independent Claim 1 about the "signal that may be provided to external circuitry." Appx68-69.

(51 of 158)

Further, as will be explained in Section V(D) below, Atkinson has no teachings regarding overheating risk, thermal stress, or "monitor[ing]," has no active external circuitry to do such monitoring, and involved a "sleep" situation in which power dissipation was orders of magnitude below what it is during operation.